Sure.

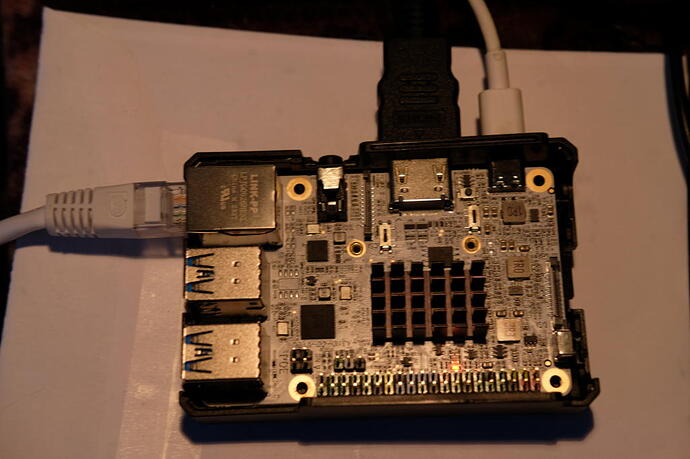

The two devices are only needed to do the reflash since it would not boot. Now that the flash is redone. It boots fine from the onboard SPI flash to the OS in the SD slot. Here is the console log:

G12B:BL:6e7c85:2a3b91;FEAT:E0F83180:402000;POC:B;RCY:0;SPINOR:0;0.

bl2_stage_init 0x01

bl2_stage_init 0x81

hw id: 0x0000 - pwm id 0x01

bl2_stage_init 0xc1

bl2_stage_init 0x02

L0:00000000

L1:20000703

L2:00008067

L3:14000000

B2:00402000

B1:e0f83180

TE: 58159

BL2 Built : 15:22:05, Aug 28 2019. g12b g1bf2b53 - luan.yuan@droid15-sz

Board ID = 1

Set A53 clk to 24M

Set A73 clk to 24M

Set clk81 to 24M

A53 clk: 1200 MHz

A73 clk: 1200 MHz

CLK81: 166.6M

smccc: 00012ab5

DDR driver_vesion: LPDDR4_PHY_V_0_1_18 build time: Aug 28 2019 15:22:01

board id: 1

Load FIP HDR from SPI, src: 0x00010000, des: 0xfffd0000, size: 0x00004000, part: 0

fw parse done

Load ddrfw from SPI, src: 0x00030000, des: 0xfffd0000, size: 0x0000c000, part: 0

Load ddrfw from SPI, src: 0x00014000, des: 0xfffd0000, size: 0x00004000, part: 0

PIEI prepare done

fastboot data load

fastboot data verify

verify result: 266

Cfg max: 1, cur: 1. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 1584MHz

Load ddrfw from SPI, src: 0x00018000, des: 0xfffd0000, size: 0x0000c000, part: 0

dmc_version 0001

Check phy result

INFO : End of CA training

INFO : End of initialization

INFO : Training has run successfully!

Check phy result

INFO : End of initialization

INFO : End of read enable training

INFO : End of fine write leveling

INFO : End of Write leveling coarse delay

INFO : Training has run successfully!

Check phy result

INFO : End of initialization

INFO : End of read dq deskew training

INFO : End of MPR read delay center optimization

INFO : End of write delay center optimization

INFO : End of read delay center optimization

INFO : End of max read latency training

INFO : Training has run successfully!

1D training succeed

Load ddrfw from SPI, src: 0x00024000, des: 0xfffd0000, size: 0x0000c000, part: 0

Check phy result

INFO : End of initialization

INFO : End of 2D read delay Voltage center optimization

INFO : End of 2D read delay Voltage center optimization

INFO : End of 2D write delay Voltage center optimization

INFO : End of 2D write delay Voltage center optimization

INFO : Training has run successfully!

channel==0

RxClkDly_Margin_A0==98 ps 10

TxDqDly_Margin_A0==98 ps 10

RxClkDly_Margin_A1==98 ps 10

TxDqDly_Margin_A1==108 ps 11

TrainedVREFDQ_A0==74

TrainedVREFDQ_A1==74

VrefDac_Margin_A0==25

DeviceVref_Margin_A0==40

VrefDac_Margin_A1==25

DeviceVref_Margin_A1==40

channel==1

RxClkDly_Margin_A0==88 ps 9

TxDqDly_Margin_A0==98 ps 10

RxClkDly_Margin_A1==88 ps 9

TxDqDly_Margin_A1==98 ps 10

TrainedVREFDQ_A0==77

TrainedVREFDQ_A1==77

VrefDac_Margin_A0==24

DeviceVref_Margin_A0==37

VrefDac_Margin_A1==22

DeviceVref_Margin_A1==37

dwc_ddrphy_apb_wr((0<<20)|(2<<16)|(0<<12)|(0xb0):0004

soc_vref_reg_value 0x 00000018 00000017 00000017 00000016 00000019 00000016 00000018 00000018 00000017 00000018 00000017 00000018 00000016 00000018 00000017 00000018 00000017 00000018 00000019 00000017 00000017 00000017 00000016 00000016 00000018 00000017 00000019 00000017 00000019 00000016 00000017 00000017 dram_vref_reg_value 0x 0000005f

2D training succeed

aml_ddr_fw_vesion: LPDDR4_PHY_V_0_1_18 build time: Aug 28 2019 13:54:19

auto size-- 65535DDR cs0 size: 2048MB

DDR cs1 size: 2048MB

DMC_DDR_CTRL: 00e00024DDR size: 3928MB

cs0 DataBus test pass

cs1 DataBus test pass

cs0 AddrBus test pass

cs1 AddrBus test pass

100bdlr_step_size ps== 432

result report

boot times 0Enable ddr reg access

Load FIP HDR from SPI, src: 0x00010000, des: 0x01700000, size: 0x00004000, part: 0

Load BL3X from SPI, src: 0x0003c000, des: 0x0172c000, size: 0x000c4000, part: 0

0.0;M3 CHK:0;cm4_sp_mode 0

MVN_1=0x00000000

MVN_2=0x00000000

[Image: g12b_v1.1.3390-6ac5299 2019-09-26 14:10:05 luan.yuan@droid15-sz]

OPS=0x10

ring efuse init

chipver efuse init

29 0b 10 00 01 14 25 00 00 11 38 33 33 42 42 50

[0.018960 Inits done]

secure task start!

high task start!

low task start!

run into bl31

NOTICE: BL31: v1.3(release):4fc40b1

NOTICE: BL31: Built : 15:58:17, May 22 2019

NOTICE: BL31: G12A normal boot!

NOTICE: BL31: BL33 decompress pass

ERROR: Error initializing runtime service opteed_fast

U-Boot 2024.01+ (Jan 24 2024 - 00:10:13 -0500) Libre Computer AML-A311D-CC

Model: Libre Computer AML-A311D-CC Alta

SoC: Amlogic Meson G12B (A311D) Revision 29:b (10:2)

DRAM: 2 GiB (effective 3.8 GiB)

Core: 408 devices, 31 uclasses, devicetree: separate

WDT: Not starting watchdog@f0d0

MMC: mmc@ffe05000: 1, mmc@ffe07000: 0

Loading Environment from FAT… Card did not respond to voltage select! : -110

** Bad device specification mmc 0 **

Card did not respond to voltage select! : -110

** Bad device specification mmc 0 **

Couldn’t find partition mmc 0

Card did not respond to voltage select! : -110

** Bad device specification mmc 0 **

Couldn’t find partition mmc 0

Error: could not access storage.

Net: eth0: ethernet@ff3f0000

starting USB…

Bus usb@ff500000: Register 3000140 NbrPorts 3

Starting the controller

USB XHCI 1.10

scanning bus usb@ff500000 for devices… 6 USB Device(s) found

scanning usb for storage devices… 0 Storage Device(s) found

Hit any key to stop autoboot: 0

Scanning for bootflows in all bootdevs

Seq Method State Uclass Part Name Filename

Scanning global bootmeth ‘efi_mgr’:

Card did not respond to voltage select! : -110

Scanning bootdev ‘mmc@ffe07000.bootdev’:

Card did not respond to voltage select! : -110

Scanning bootdev ‘mmc@ffe05000.bootdev’:

0 efi ready mmc 1 mmc@ffe05000.bootdev.part efi/boot/bootaa64.efi

** Booting bootflow ‘mmc@ffe05000.bootdev.part_1’ with efi

Booting /efi\boot\bootaa64.efi

Welcome to GRUB!